在大规模ASIC或FPGA设计中,多时钟系统往往是不可避免的,这样就产生了不同时钟域数据传输的问题,其中一个比较好的解决方案就是使用异步FIFO来作不同时钟域数据传输的缓冲区,这样既可以使相异时钟域数据传输的时序...

”CDC 异步fifo设计“ 的搜索结果

FPGA -手写异步FIFO

标签: fpga开发

在处理跨时钟域时,转换为格雷码处理。

set_max_delay [-datapath_only] -from [ node_list] -to [node_list] delay_value

对异步FIFO的一些简单验证

通常对异步FIFO的格雷码下约束有两个原因,一个是保证异步FIFO的性能,如果格雷码跨异步的delay太长,FIFO传输数据的效率会下降,另一个是保证多比特格雷码在跨时钟域时不会采错,如果不同bit之间的delay不一致,就...

【牛客】VL45 异步FIFO

CDC处理——异步FIFO

标签: 前端

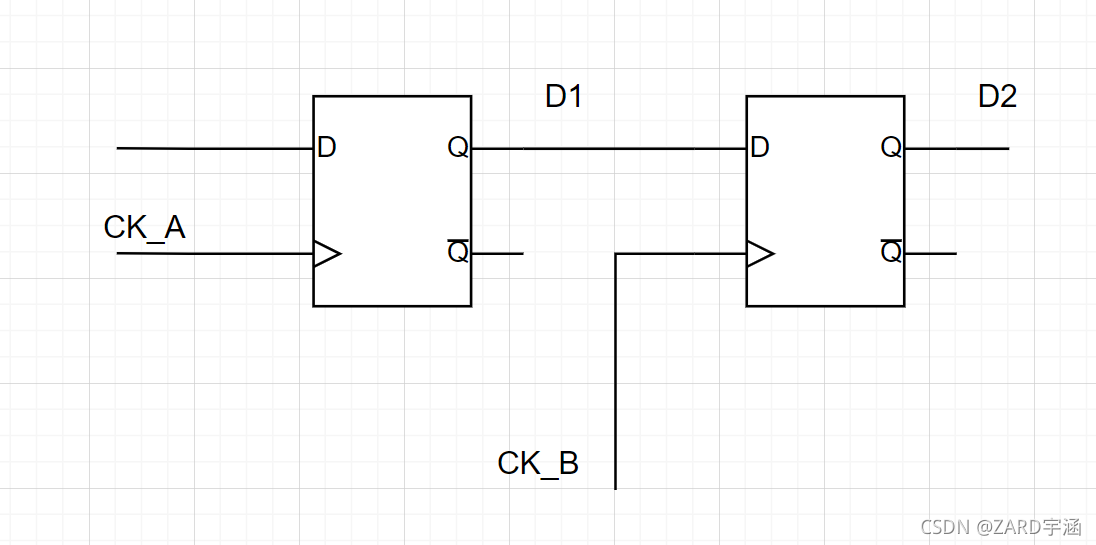

异步FIFO的关键就在于读写指针跨时钟域传输的问题,保证每次跳变仅 有1bit变化,这样无论是变化前还是变化后的读写指针被同步到另一个时钟域,都不会发生“FIFO空时继续读”、“FIFO满时继续写”这样的逻辑错误。...

/write时钟域中时钟信号,复位信号,wr使能信号,wdata写入数据。

面试——异步FIFO详解

标签: 面试

一开始是想既然是极简教程,就应该只给出FIFO的概念,没想到还是给出了同步以及异步FIFO的设计,要不然总感觉内容不完整,也好,自己设计的FIFO模块不用去担心因IP核跨平台不通用的缺陷!那我们开始吧。

异步FIFO模块验证-面试总结

标签: 面试

IC验证面试之异步FIFO模块验证面试总结

异步FIFO的空满判断有很多方法,但其中不变的一个点是,利用格雷码减少亚稳态发生的概率,在这个基础上可以得到,将二进制地址转换成格雷码后,满信号基于写时钟域来判断,此时同步过来的读地址信号有一定的延迟,即...

异步FIFO设计与实现及相关问题

标签: fpga

异步fifo读写分别采用不同的时钟,可以用来跨时钟域。也可以进行数据输入输出的位宽转换。 FIFO的深度计算 数据突发长度(burst length): 模块A向FIFO中写入数据,模块B从FIFO中不间断的读出数据,模块A...

跨时钟域信号处理方法&异步FIFO

标签: 学习

https://blog.csdn.net/times_poem/article/details/73437984一、来自cnblogs...异步fifo的设计(FPGA)http://www.cnblogs.com/aslmer/p/6114216.html异步FIFO的FPGA实现http://www.cnblogs.com/BitArt/archive/2013...

本文更新了过去对异步FIFO的设计!

推荐文章

- Python菜鸟晋级04----raw_input() 与 input()的区别_pycharm没有raw input-程序员宅基地

- 高通AR增强现实多卡识别和扩展跟踪Unity_imagetarget扩展追踪-程序员宅基地

- 对于三星手机的手工root方法-程序员宅基地

- 2021年佛山高考成绩查询,2021年高三佛山一模,看佛山高中排名-程序员宅基地

- 删除并清空应收应付模块 期初数据_应付管理系统怎么清除数据-程序员宅基地

- 嵌入式固件加密的几种方式-程序员宅基地

- 非root情况下访问手机存储位置权限的方法_不root 通讯录 存放目录-程序员宅基地

- Mybatis项目开发流程_使用mybatis的开发步骤-程序员宅基地

- 三方协议,档案,工龄,保险,户口,-程序员宅基地

- 华为交换机命令 端口速率_华为S5700交换机的端口QOS限速问题-程序员宅基地